5月17日消息,台积电在2024欧洲技术研讨会上隆重登场,分享了其最新的技术成果。会议期间,台积电特别展示了其采用前沿12FFC+(基于12纳米工艺)与尖端N5(5纳米工艺)技术相结合所开发的HBM4基础芯片。

翻译台积电设计与技术平台高级总监内容如下:

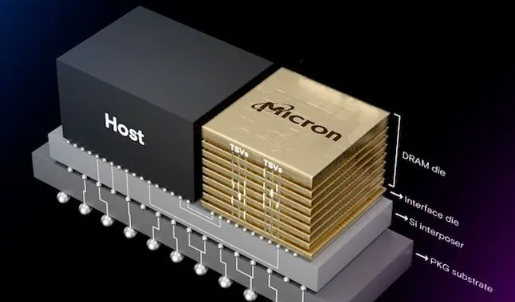

我们正与主要的 HBM 存储器合作伙伴(美光、三星、SK hynix)合作,在先进节点上实现 HBM4 全堆栈集成。12FFC+ 基础 Dies 在满足 HBM 性能要求的情况下具备成本优势,而 N5 基础 Dies 又可以在更低功耗下达到 HBM4 预期速度。

采用台积电 12FFC+ 工艺(源自该公司成熟的 16 纳米 FinFET 技术)制造的基础芯片将能够构建 12-Hi 和 16-Hi HBM4 存储器堆栈,容量分别为 48 GB 和 64 GB。

使用 12FFC+ 工艺将实现 "高性价比" 的基础芯片,这些芯片将使用硅内插件将内存连接到主机处理器。

文明上网,理性发言,共同做网络文明传播者