5月20日消息,随着人工智能(AI)芯片市场的急剧扩张,对更大规模硅中介层的需求显著上升,这直接引发了12英寸晶圆在切割过程中的产出量缩减问题,进而对CoWoS(Chip-on-Wafer-on-Substrate)高级封装技术的产能形成了巨大压力,需求与供应之间的缺口进一步拉大。

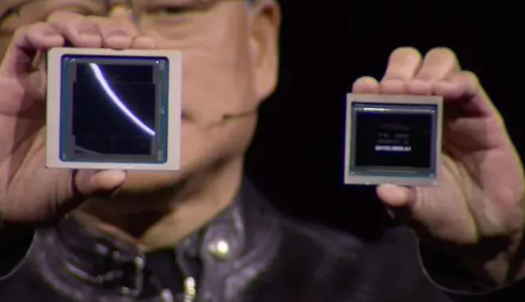

芯片变大

集邦咨询预估英伟达推出的 B 系列(包括 GB200、B100、B200),将消耗更多的 CoWoS 封装产能。

此前报道,台积电增加了 2024 年全年的 CoWoS 产能需求,预计到年底月产能将接近 4 万片,相比 2023 年的总产能增长超过 150%。2025 年的总产能有可能增长近一倍。

不过英伟达发布的 B100 和 B200 芯片,中间层面积(interposer area)将比以前更大,意味着 12 英寸晶圆切割出来的芯片数量减少,导致 CoWoS 的产能无法满足 GPU 需求。

HBM

业内人士表示 HBM 也是一大难题,采用 EUV 层数开始逐步增加,以 HBM 市占率第一的 SK 海力士为例,该公司于 1α 生产时应用单层 EUV,今年开始转向 1β,并有可能将 EUV 应用提升 3~4 倍。

除技术难度提升外,随着 HBM 历次迭代,HBM 中的 DRAM 数量也同步提升,堆叠于 HBM2 中的 DRAM 数量为 4~8 个,HBM3/3E 则增加到 8~12 个,HBM4 中堆叠的 DRAM 数量将增加到 16 个。

文明上网,理性发言,共同做网络文明传播者